# RS520A-E11-RS24U

# **2U Rackmount Server User Guide**

E19358 Revised Edition V3 September 2021

## Copyright © 2021 ASUSTeK COMPUTER INC. All Rights Reserved.

No part of this manual, including the products and software described in it, may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language in any form or by any means, except documentation kept by the purchaser for backup purposes, without the express written permission of ASUSTEK COMPUTER INC. ("ASUS").

ASUS provides this manual "as is" without warranty of any kind, either express or implied, including but not limited to the implied warranties or conditions of merchantability or fitness for a particular purpose. In no event shall ASUS, its directors, officers, employees, or agents be liable for any indirect, special, incidental, or consequential damages (including damages for loss of profits, loss of business, loss of use or data, interruption of business and the like), even if ASUS has been advised of the possibility of such damages arising from any defect or error in this manual or product.

Specifications and information contained in this manual are furnished for informational use only, and are subject to change at any time without notice, and should not be construed as a commitment by ASUS. ASUS assumes no responsibility or liability for any errors or inaccuracies that may appear in this manual, including the products and software described in it.

Product warranty or service will not be extended if: (1) the product is repaired, modified or altered, unless such repair, modification of alteration is authorized in writing by ASUS; or (2) the serial number of the product is defaced or missing.

Products and corporate names appearing in this manual may or may not be registered trademarks or copyrights of their respective companies, and are used only for identification or explanation and to the owners' benefit, without intent to infringe.

| Safety | y informat  | ion                                                                                    | vii  |  |  |

|--------|-------------|----------------------------------------------------------------------------------------|------|--|--|

| About  | t this guid | e                                                                                      | ix   |  |  |

| Chap   | ter 1: Pro  | oduct Introduction                                                                     |      |  |  |

| 1.1    | System      | System package contents                                                                |      |  |  |

| 1.2    | Serial r    | Serial number label                                                                    |      |  |  |

| 1.3    | System      | specifications                                                                         | 1-4  |  |  |

| 1.4    | Front p     | anel features                                                                          | 1-7  |  |  |

| 1.5    | Rear pa     | anel features                                                                          | 1-7  |  |  |

| 1.6    | Interna     | I features                                                                             | 1-8  |  |  |

| 1.7    | LED inf     | formation                                                                              | 1-9  |  |  |

|        | 1.7.1       | Front panel LEDs                                                                       | 1-9  |  |  |

|        | 1.7.2       | Storage device status LED                                                              | 1-10 |  |  |

|        | 1.7.3       | LAN (RJ-45) LEDs                                                                       | 1-11 |  |  |

|        | 1.7.4       | Rear panel LEDs                                                                        | 1-11 |  |  |

|        | 1.7.5       | Q-Code table                                                                           | 1-12 |  |  |

| Chap   | ter 2: Ha   | rdware Information                                                                     |      |  |  |

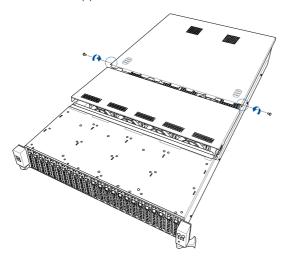

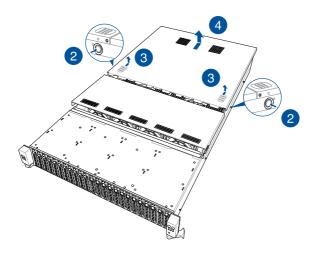

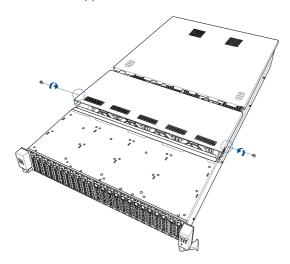

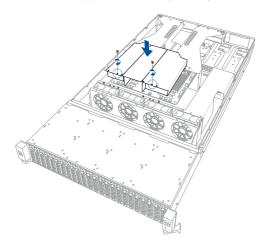

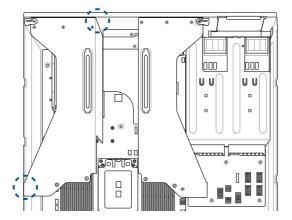

| 2.1    | Chassi      | s cover                                                                                | 2-2  |  |  |

|        | 2.1.1       | Removing the rear cover                                                                | 2-2  |  |  |

|        | 2.1.2       | Removing the mid cover                                                                 | 2-3  |  |  |

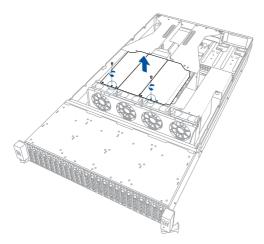

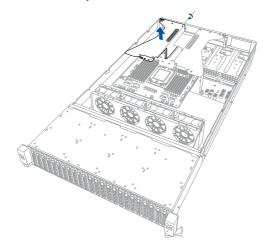

| 2.2    | Air duc     | ts                                                                                     | 2-4  |  |  |

|        | 2.2.1       | Removing the air ducts                                                                 | 2-4  |  |  |

|        | 2.2.2       | Installing the air ducts                                                               | 2-4  |  |  |

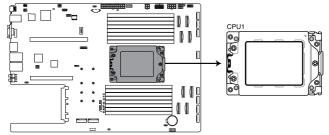

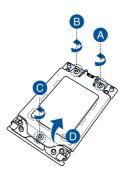

| 2.3    | Central     | Processing Unit (CPU)                                                                  | 2-5  |  |  |

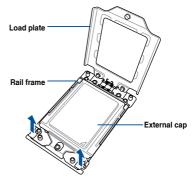

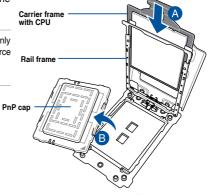

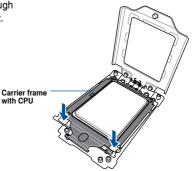

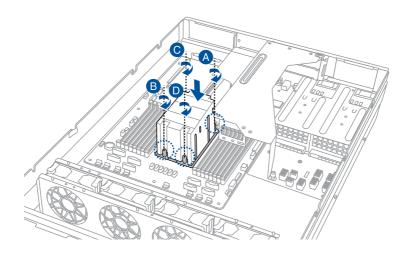

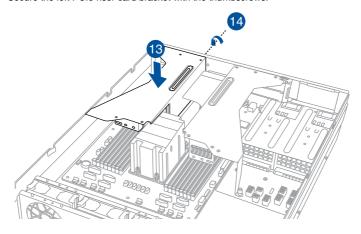

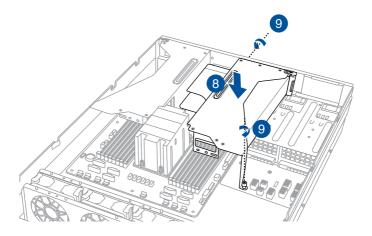

|        | 2.3.1       | Installing the CPU and heatsink                                                        | 2-5  |  |  |

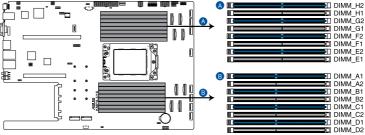

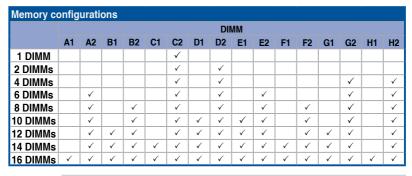

| 2.4    | System      | n memory                                                                               | 2-10 |  |  |

|        | 2.4.1       | Overview                                                                               | 2-10 |  |  |

|        | 2.4.2       | Memory Configurations                                                                  | 2-10 |  |  |

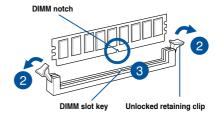

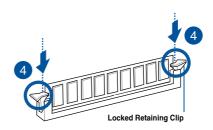

|        | 2.4.3       | Installing a DIMM                                                                      | 2-11 |  |  |

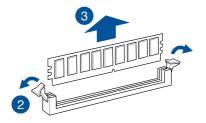

|        | 2.4.4       | Removing a DIMM                                                                        | 2-11 |  |  |

| 2.5    | Storage     | e devices                                                                              | 2-12 |  |  |

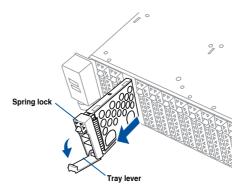

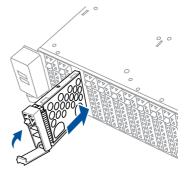

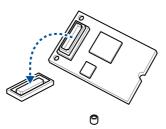

|        | 2.5.1       | Installing a 2.5" hot-swap SATA/SAS/NVMe storage device                                | 2-12 |  |  |

| 2.6    | Expans      | sion slot                                                                              | 2-14 |  |  |

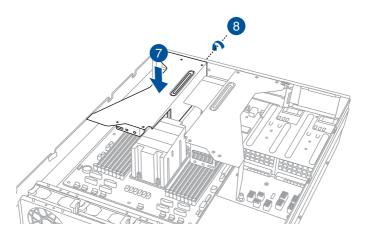

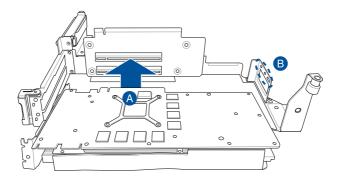

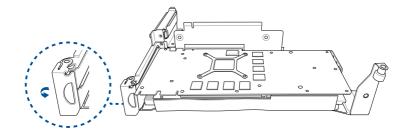

|        | 2.6.1       | Installing an expansion card to the left PCle riser card bract (on selected models)    |      |  |  |

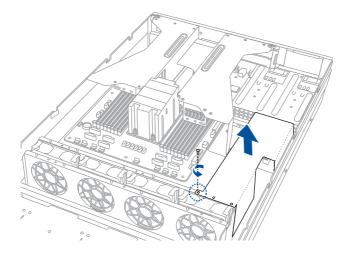

|        | 2.6.2       | Installing an expansion card to the right PCle riser card bra-<br>(on selected models) |      |  |  |

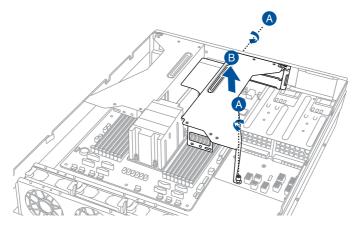

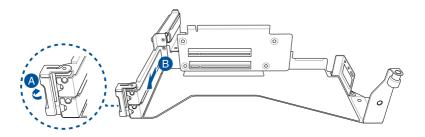

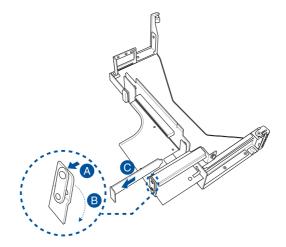

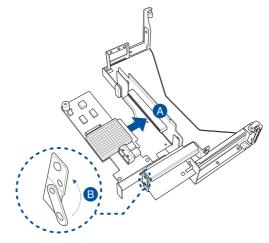

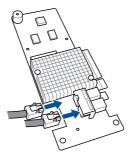

|      | 2.6.3      | Installing a ASUS PIKE II card to the right PCIe riser card bracket     | 2-22 |

|------|------------|-------------------------------------------------------------------------|------|

|      | 2.6.4      | Installing an OCP 3.0 card to the OCP 3.0 slot                          |      |

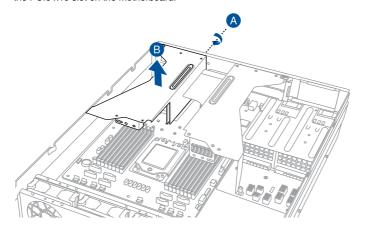

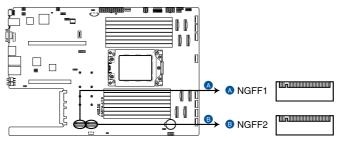

|      | 2.6.5      | Installing an M.2 (NGFF) card                                           |      |

|      | 2.6.6      | (optional) Installing the PFR module                                    | 2-27 |

|      | 2.6.7      | Configuring an expansion card                                           | 2-28 |

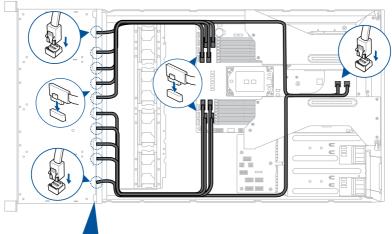

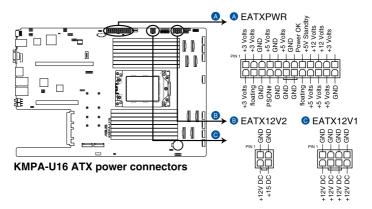

| 2.7  | Cable c    | onnections                                                              | 2-29 |

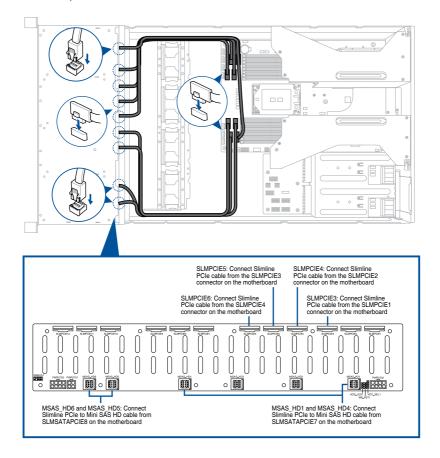

| 2.8  | Backpla    | ane cabling                                                             | 2-30 |

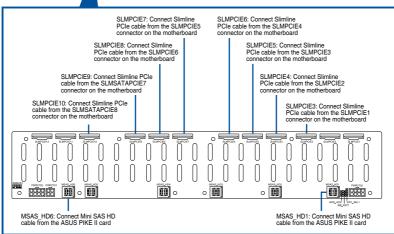

| 2.9  | Storage    | device configuration and cabling                                        | 2-31 |

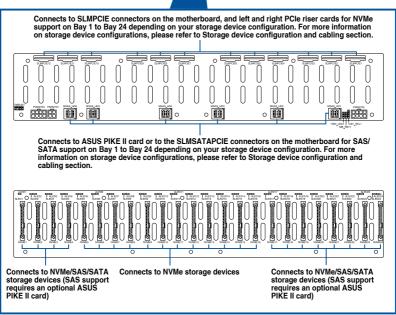

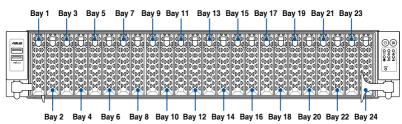

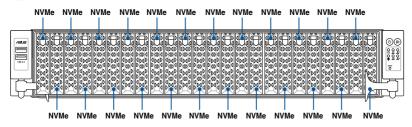

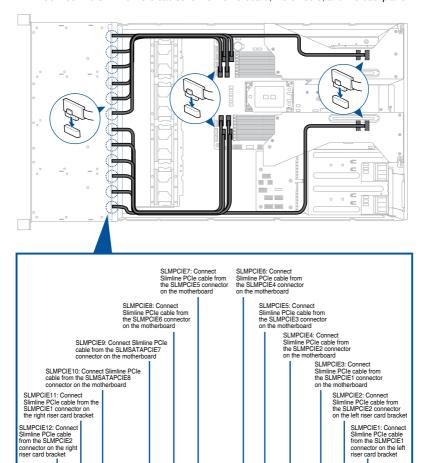

|      | 2.9.1      | 24 x NVMe storage device configuration and cabling (on selected models) | 2-32 |

|      | 2.9.2      | 16 x NVMe and 8 x SAS/SATA storage device configuration and cabling     | 2-34 |

|      | 2.9.3      | 12 x NVMe and 12 x SAS/SATA storage device configuration and cabling    |      |

| 2.10 | Remova     | able/optional components                                                | 2-38 |

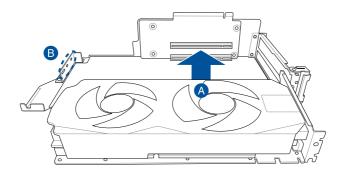

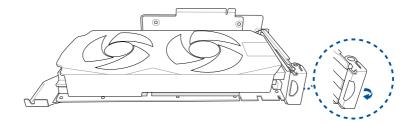

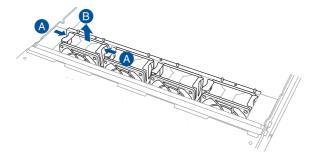

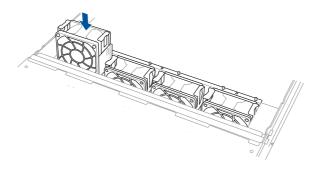

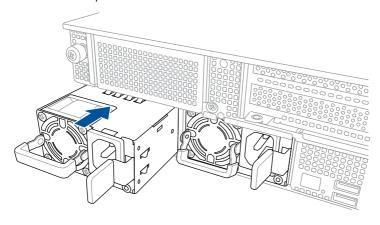

|      | 2.10.1     | System fans                                                             | 2-38 |

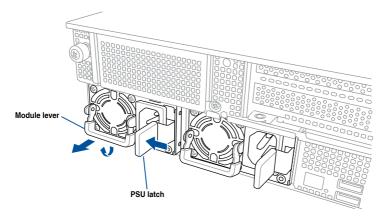

|      | 2.10.2     | Redundant power supply module                                           | 2-40 |

| Chap | ter 3: Ins | tallation Options                                                       |      |

| 3.1  | Tool-les   | ss Friction Rail Kit                                                    | 3-2  |

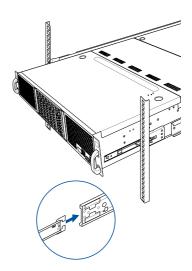

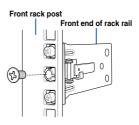

|      | 3.1.1      | Installing the tool-less rack rail                                      | 3-2  |

|      | 3.1.2      | Rail kit dimensions                                                     | 3-4  |

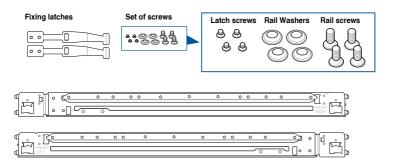

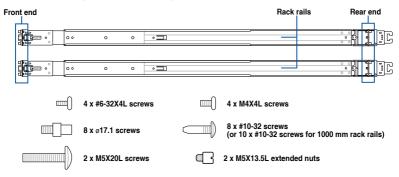

| 3.2  | Ball bea   | aring Rail Kit                                                          | 3-5  |

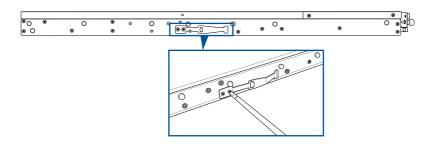

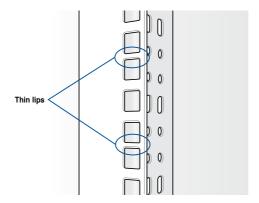

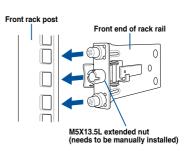

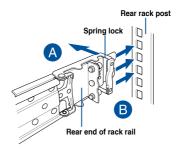

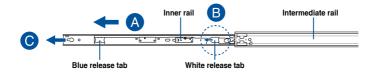

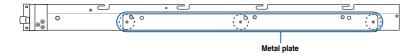

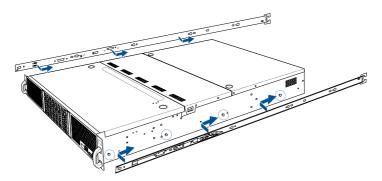

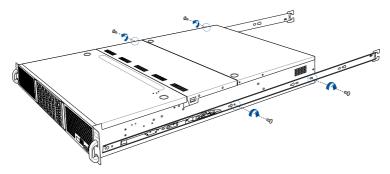

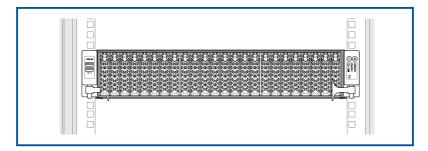

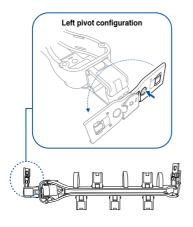

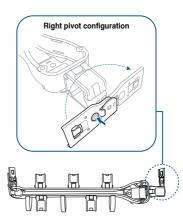

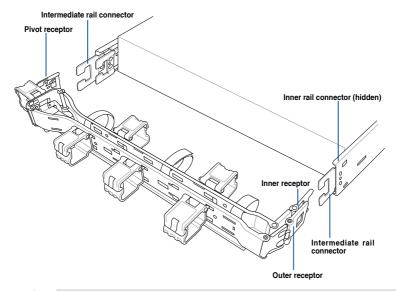

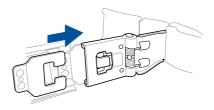

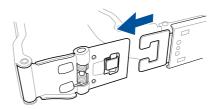

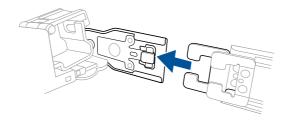

|      | 3.2.1      | Attaching the rack rails                                                | 3-6  |

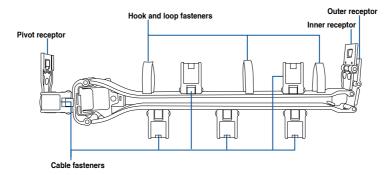

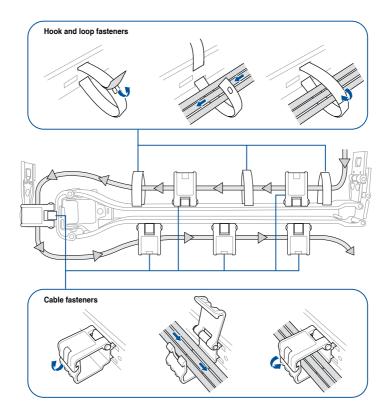

| 3.3  | Cable m    | nanagement arm (optional for 1200 mm rack rails)                        |      |

|      | 3.3.1      | Attaching the cable management arm                                      | 3-11 |

| Chap | ter 4: Mo  | therboard Information                                                   |      |

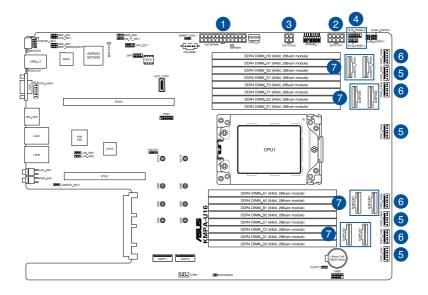

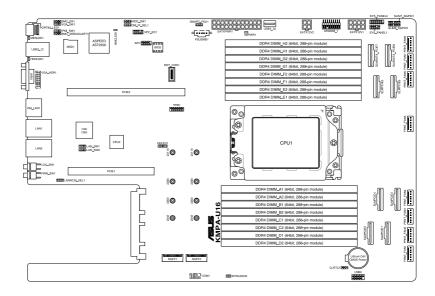

| 4.1  | Mother     | ooard layout                                                            | 4-2  |

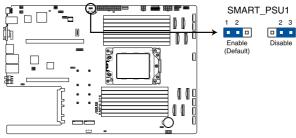

| 4.2  | Jumper     | s                                                                       | 4-5  |

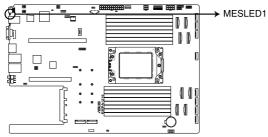

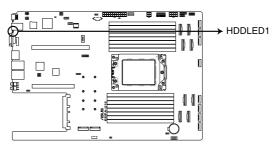

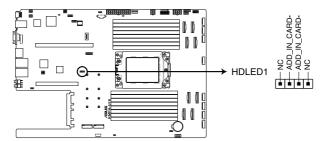

| 4.3  | Internal   | LEDs                                                                    | 4-10 |

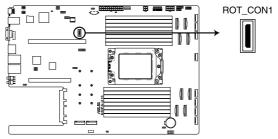

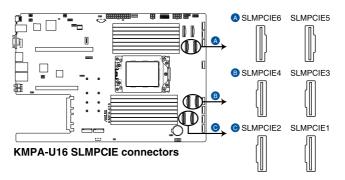

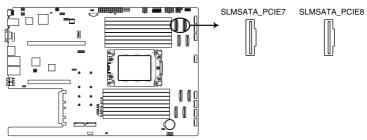

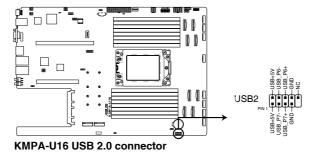

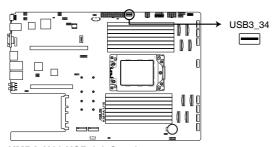

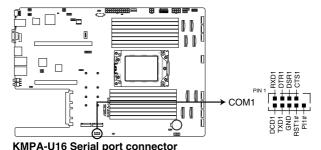

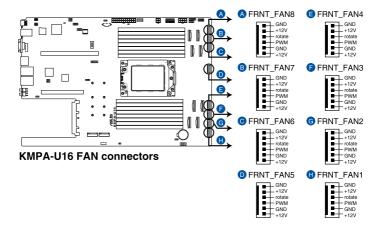

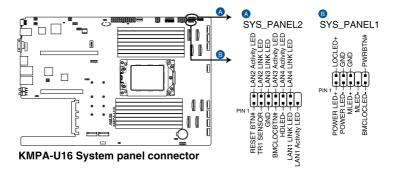

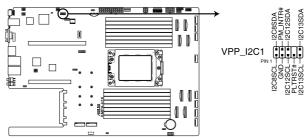

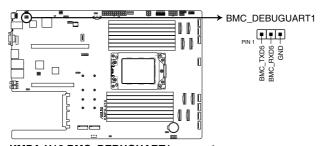

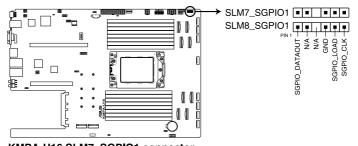

| 4.4  | Internal   | connectors                                                              | 4-12 |

| Chap | ter 5: BIC | OS Setup                                                                |      |

| 5.1  | Managii    | ng and updating your BIOS                                               | 5-2  |

|      | 5.1.1      | ASUS CrashFree BIOS 3 utility                                           |      |

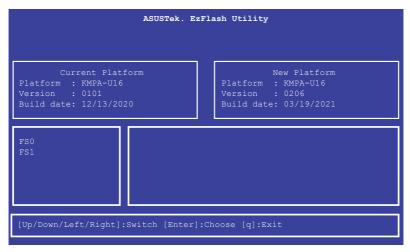

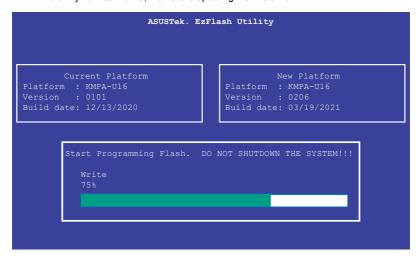

|      | 5.1.2      | ASUS EZ Flash Utility                                                   | 5-3  |

|      | 5.1.3      | BUPDATER utility                                                        | 5-4  |

| 5.2  | BIOS se            | etup program5-                     | 6  |  |

|------|--------------------|------------------------------------|----|--|

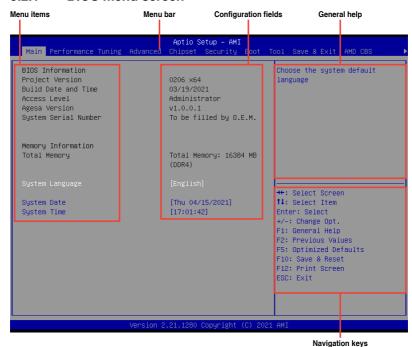

|      | 5.2.1              | BIOS menu screen5-                 | -7 |  |

|      | 5.2.2              | Menu bar5-                         | 7  |  |

|      | 5.2.3              | Menu items5-                       | -8 |  |

|      | 5.2.4              | Submenu items5-                    | -8 |  |

|      | 5.2.5              | Navigation keys5-                  | 8  |  |

|      | 5.2.6              | General help5-                     | 8  |  |

|      | 5.2.7              | Configuration fields5-             | 8  |  |

|      | 5.2.8              | Pop-up window5-                    | 8  |  |

|      | 5.2.9              | Scroll bar5-                       | 8  |  |

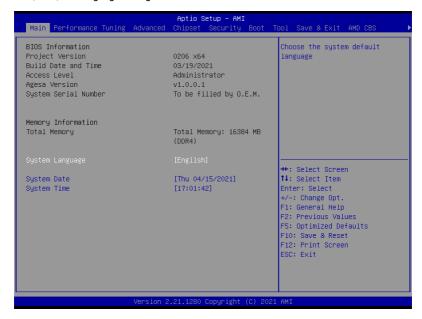

| 5.3  | Main me            | enu5-                              | .9 |  |

|      | 5.3.1              | System Language [English]5-        | 9  |  |

|      | 5.3.2              | System Date [Day xx/xx/xxxx]5-     | 9  |  |

|      | 5.3.3              | System Time [xx:xx:xx]5-           | 9  |  |

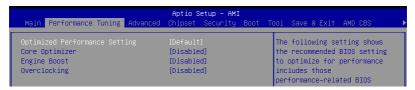

| 5.4  | Perform            | nance Tuning menu5-1               | 0  |  |

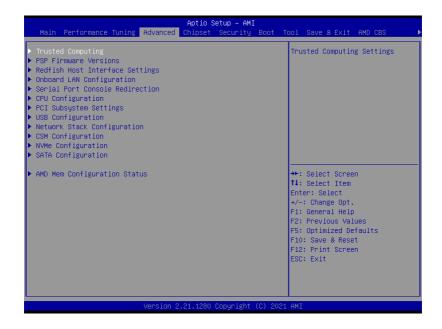

| 5.5  | Advanc             | ed menu5-1                         | 1  |  |

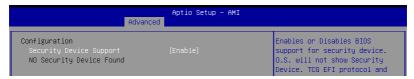

|      | 5.5.1              | Trusted Computing5-1               | 2  |  |

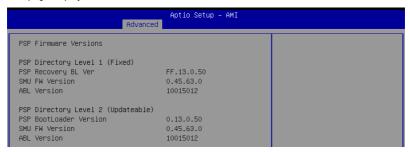

|      | 5.5.2              | PSP Firmware Versions5-1           | 2  |  |

|      | 5.5.3              | Redfish Host Interface Settings5-1 | 2  |  |

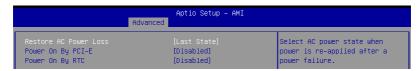

|      | 5.5.4              | APM Configuration5-1               | 3  |  |

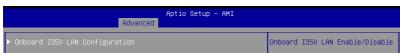

|      | 5.5.5              | Onboard LAN Configuration5-1       | 3  |  |

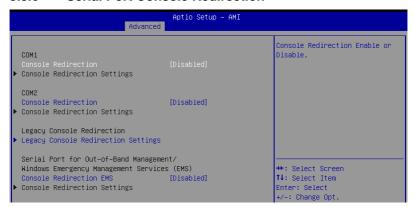

|      | 5.5.6              | Serial Port Console Redirection5-1 | 4  |  |

|      | 5.5.7              | CPU Configuration5-1               | 7  |  |

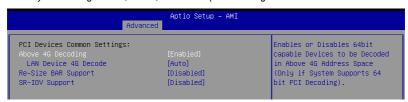

|      | 5.5.8              | PCI Subsystem Settings5-1          | 7  |  |

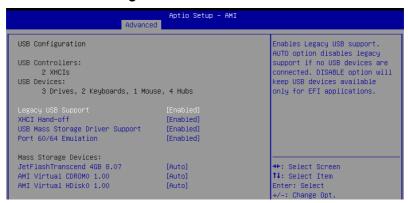

|      | 5.5.9              | USB Configuration5-1               | 8  |  |

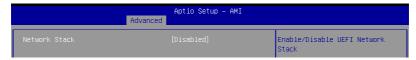

|      | 5.5.10             | Network Stack Configuration5-1     | 9  |  |

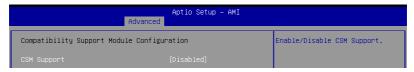

|      | 5.5.11             | CSM Configuration5-2               | 0  |  |

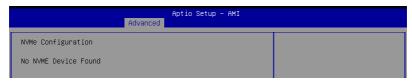

|      | 5.5.12             | NVMe Configuration5-2              | 1  |  |

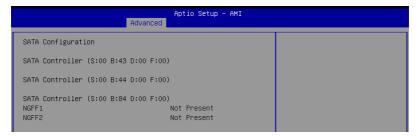

|      | 5.5.13             | SATA Configuration5-2              | 2  |  |

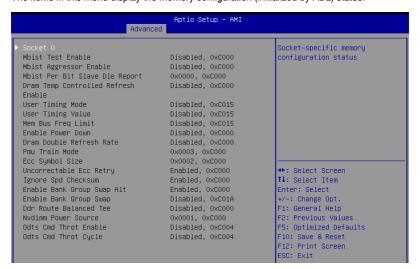

|      | 5.5.14             | AMD Mem Configuration Status5-2    | 2  |  |

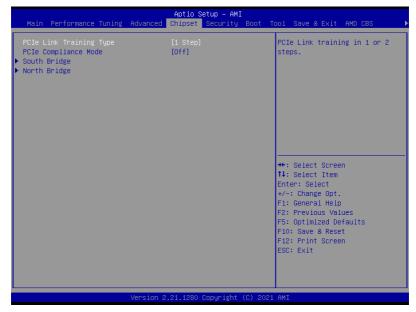

| 5.6  | Chipset            | menu5-2                            | 3  |  |

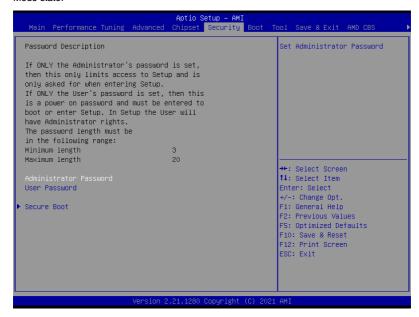

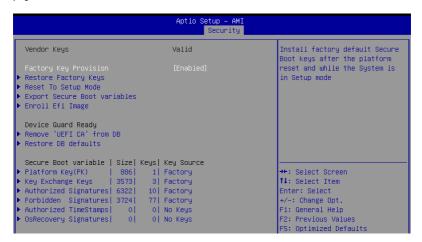

| 5.7  | Security           | y menu5-2                          | 6  |  |

| 5.8  | Boot me            | enu5-3                             | 0  |  |

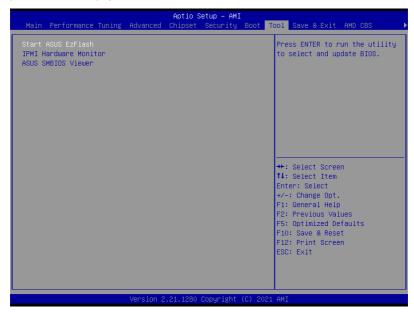

| 5.9  | Tool menu5         |                                    |    |  |

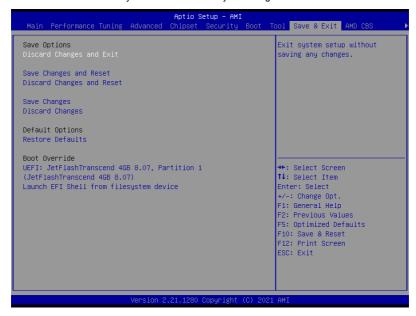

| 5.10 | Save & Exit menu5- |                                    |    |  |

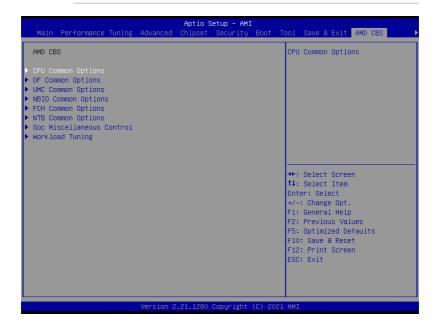

| 5.11   | AMD CBS menu5-33        |                                  |      |  |  |

|--------|-------------------------|----------------------------------|------|--|--|

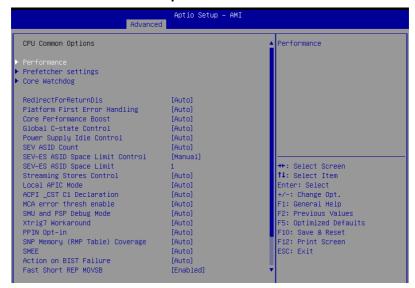

|        | 5.11.1                  | CPU Common Options               | 5-34 |  |  |

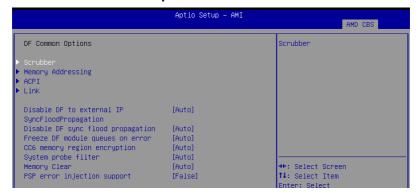

|        | 5.11.2                  | DF Common Options                | 5-39 |  |  |

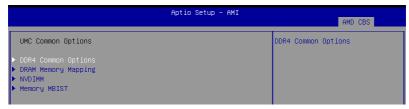

|        | 5.11.3                  | UMC Common Option                | 5-42 |  |  |

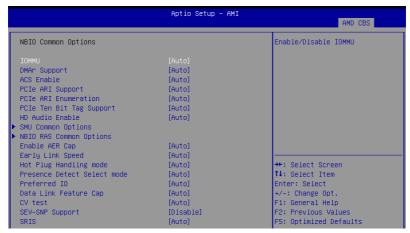

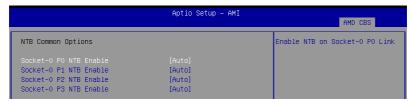

|        | 5.11.4                  | NBIO Common Options              | 5-53 |  |  |

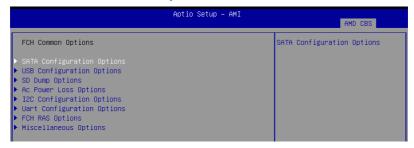

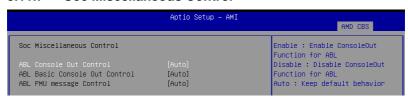

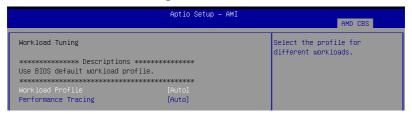

|        | 5.11.5                  | FCH Common Options               | 5-60 |  |  |

|        | 5.11.6                  | NTB Common Options               | 5-65 |  |  |

|        | 5.11.7                  | Soc Miscellaneous Control        | 5-67 |  |  |

|        | 5.11.8                  | Workload Tuning5                 | 5-68 |  |  |

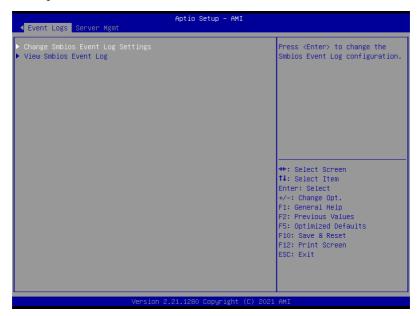

| 5.12   | Event Lo                | ogs menu5                        | 5-69 |  |  |

|        | 5.12.1                  | Change Smbios Event Log Settings | 5-69 |  |  |

|        | 5.12.2                  | View Smbios Event Log            | 5-70 |  |  |

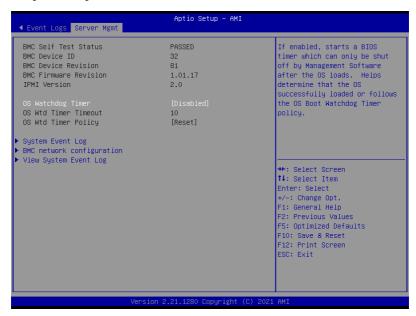

| 5.13   | Server M                | Igmt menu                        | 5-71 |  |  |

| Chapte | er 6: Driv              | ver Installation                 |      |  |  |

| 6.1    | Running the Support DVD |                                  |      |  |  |

| Appen  | dix                     |                                  |      |  |  |

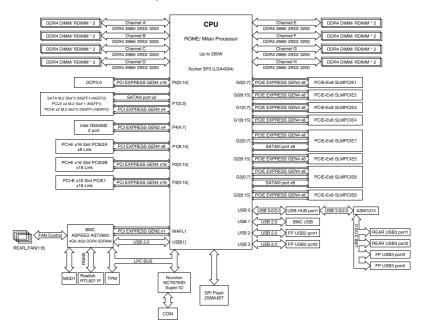

| KMPA-  | U16 block               | c diagram                        | A-2  |  |  |

|        |                         | -                                |      |  |  |

|        |                         | port                             |      |  |  |

# Safety information

# **Electrical Safety**

- Before installing or removing signal cables, ensure that the power cables for the system unit and all attached devices are unplugged.

- To prevent electrical shock hazard, disconnect the power cable from the electrical outlet before relocating the system.

- When adding or removing any additional devices to or from the system, ensure that the

power cables for the devices are unplugged before the signal cables are connected. If

possible, disconnect all power cables from the existing system before you add a device.

- If the power supply is broken, do not try to fix it by yourself. Contact a qualified service technician or your dealer.

## **Operation Safety**

- Any mechanical operation on this server must be conducted by certified or experienced engineers.

- Before operating the server, carefully read all the manuals included with the server package.

- Before using the server, ensure all cables are correctly connected and the power cables are not damaged. If any damage is detected, contact your dealer as soon as possible.

- To avoid short circuits, keep paper clips, screws, and staples away from connectors, slots, sockets and circuitry.

- Avoid dust, humidity, and temperature extremes. Place the server on a stable surface.

- If you encounter technical problems with the product, contact a qualified service technician or your retailer.

This product is equipped with a three-wire power cable and plug for the user's safety. Use the power cable with a properly grounded electrical outlet to avoid electrical shock.

# Lithium-Ion Battery Warning

CAUTION! Danger of explosion if battery is incorrectly replaced. Replace only with the same or equivalent type recommended by the manufacturer. Dispose of used batteries according to the manufacturer's instructions.

# Heavy System -

CAUTION! This server system is heavy. Ask for assistance when moving or carrying the system.

# **Optical Drive Safety Information**

## **Laser Safety Information**

To prevent exposure to the optical drive's laser, do not attempt to disassemble or repair the optical drive by yourself. For your safety, contact a professional technician for assistance.

# About this guide

## **Audience**

This user guide is intended for system integrators, and experienced users with at least basic knowledge of configuring a server.

## **Contents**

This guide contains the following parts:

## 1. Chapter 1: Product Introduction

This chapter describes the general features of the server, including sections on front panel and rear panel specifications.

## 2. Chapter 2: Hardware Information

This chapter lists the hardware setup procedures that you have to perform when installing or removing system components.

## 3. Chapter 3: Installation Options

This chapter describes how to install optional components into the barebone server.

## 4. Chapter 4: Motherboard Information

This chapter gives information about the motherboard that comes with the server. This chapter includes the motherboard layout, jumper settings, and connector locations.

## 5. Chapter 5: BIOS Setup

This chapter tells how to change system settings through the BIOS Setup menus and describes the BIOS parameters.

## 6. Chapter 6: Driver Installation

This chapter provides instructions for installing the necessary drivers for different system components.

## Conventions

To ensure that you perform certain tasks properly, take note of the following symbols used throughout this manual.

**DANGER/WARNING:** Information to prevent injury to yourself when trying to complete a task.

**CAUTION:** Information to prevent damage to the components when trying to complete a task.

**IMPORTANT:** Instructions that you MUST follow to complete a task.

NOTE: Tips and additional information to help you complete a task.

# **Typography**

**Bold text** Indicates a menu or an item to select.

Italics Used to emphasize a word or a phrase.

<Key> Keys enclosed in the less-than and greater-than sign

means that you must press the enclosed key.

Example: <Enter> means that you must press the Enter

or Return key.

<Key1>+<Key2>+<Key3> If you must press two or more keys simultaneously, the

key names are linked with a plus sign (+).

Example: <Ctrl>+<Alt>+<Del>

Command Means that you must type the command exactly as

shown, then supply the required item or value enclosed in

brackets.

Example: At the DOS prompt, type the command line:

format A:/S

#### References

Refer to the following sources for additional information, and for product and software updates.

## 1. ASUS Control Center (ACC) user guide

This manual tells how to set up and use the proprietary ASUS server management utility. Visit asuscontrolcenter asus.com for more information.

#### 2. ASUS websites

The ASUS websites provide updated information for all ASUS hardware and software products. Visit https://www.asus.com for more information.

# **Product Introduction**

This chapter describes the general features of the chassis kit. It includes sections on front panel and rear panel specifications.

# 1.1 System package contents

Check your system package for the following items.

| Model Name     | RS520A-E11-RS24U                                                                                                                                          |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chassis        | ASUS R2P-C 2U Rackmount Chassis                                                                                                                           |

| Motherboard    | ASUS KMPA-U16 Server Board                                                                                                                                |

|                | 1+1 800W 80PLUS Platinum or 850W 80PLUS Titanium or 1200W 80PLUS Platinum or 1600W 80PLUS Platinum Redundant Power Supply                                 |

| Component      | 1 x 2.5-inch Storage Device Backplane                                                                                                                     |

| ·              | 24 x 2.5-inch Storage Device Trays or Dummy Trays                                                                                                         |

|                | 4 x System Fans (80 mm x 80 mm x 38 mm)                                                                                                                   |

|                | 1 x AMD EPYC™ Support DVD                                                                                                                                 |

| Accessories    | 1 x Bag of Screws                                                                                                                                         |

| Accessories    | 1 x CPU Heatsink                                                                                                                                          |

|                | 2 x AC Power Cable                                                                                                                                        |

|                | 1 x 800W 80PLUS Platinum Power Supply <b>or</b> 1 x 850W 80PLUS Titanium Power Supply <b>or</b> 1 x 1200W/1600W 80PLUS Platinum Power Supply (Second PSU) |

| 0.18           | 2 x Riser card (16 NVMe configuration & 12 NVMe configuration)                                                                                            |

| Optional Items | System redundant fan kit                                                                                                                                  |

|                | 1 x Friction Rail Kit <b>or</b> Ball-bearing rail kit                                                                                                     |

|                | ASUS PIKE II 3008/3108 card                                                                                                                               |

|                |                                                                                                                                                           |

If any of the above items is damaged or missing, contact your retailer.

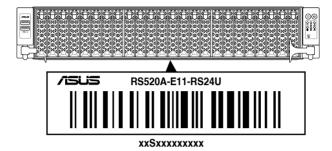

# 1.2 Serial number label

The product's serial number contains 12 characters such as xxSxxxxxxxx and printed on the sticker at the server's front cover.

The correct serial number of the product is required if you need to request for support from the ASUS Technical Support team.

# 1.3 System specifications

The ASUS RS520A-E11-RS24U features the ASUS KMPA-U16 server board. The server supports AMD EPYC™ 7002/7003 Series processors plus other latest technologies through the chipsets onboard.

| Model Name         |                               | RS520A-E11-RS24U                                                                                                                                                                                                                                            |  |  |

|--------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Motherboard        |                               | KMPA-U16                                                                                                                                                                                                                                                    |  |  |

| Processor Support  |                               | 1 x Socket SP3 (LGA 4094)  AMD EPYC™ 7002/7003 Series  xGMI (External Global Memory Interface Link)                                                                                                                                                         |  |  |

| Core Logic         |                               | System on Chip (SoC)                                                                                                                                                                                                                                        |  |  |

| Total Slots        |                               | 16 (8-channel per CPU, 16 DIMM per CPU)                                                                                                                                                                                                                     |  |  |

|                    | Capacity                      | Maximum up to 4096GB                                                                                                                                                                                                                                        |  |  |

| Memory             | Memory Type                   | DDR4 3200/2933 RDIMM/LRDIMM/3DS LRDIMM  * Please refer to <a href="www.asus.com">www.asus.com</a> for latest momory AVL update                                                                                                                              |  |  |

| ,                  | Memory Size                   | 64GB, 32GB, 16GB RDIMM 64GB, 128GB LRDIMM 64GB, 128GB, 256GB (LRDIMM 3DS/ 3DS RDIMM) * Refer to www.asus.com/support for more information                                                                                                                   |  |  |

|                    | Total PCI/PCIe/<br>PIKE Slots | Up to 5                                                                                                                                                                                                                                                     |  |  |

|                    | Slot Type                     | 24 x NVMe 1 x PCIe x16 slot (Gen4 x8 link, LP)(CPU1) (GPU card support limited)                                                                                                                                                                             |  |  |

| Expansion<br>Slots |                               | 16 x NVMe or 12 x NVMe Up to 5 PCle Gen4 slots + 1 OCP3.0 2 x PCle x16 slot (Gen4 x16 link, FHFL)(CPU1) or Dual-slot GPU cards or 4 x PCle x16 slot (Gen4 x8 link, FHFL)(CPU1) 1 x PCle x16 slot (Gen4 x8 link, LP)(CPU1) 1 x OCP 3.0 Mezzanine slot (CPU1) |  |  |

|                    | M.2                           | 2 x M.2 (Up to 22110) (CPU1)<br>(Support 2 x SATA/PCle Gen4 x2 or 1 x PCle Gen4 x4 M.2)                                                                                                                                                                     |  |  |

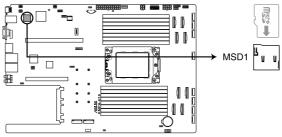

|                    | Micro SD Card slot            | 1                                                                                                                                                                                                                                                           |  |  |

|                    | Proprietary Slot 1            | 1 x PCle x16 slot (Gen4 x8 link, for pike card only)                                                                                                                                                                                                        |  |  |

| Proprietary Slot 2 |                               | -                                                                                                                                                                                                                                                           |  |  |

|                    | SATA Controller               | Integrated in CPU                                                                                                                                                                                                                                           |  |  |

| Storage            | SAS Controller                | Optional kits: ASUS PIKE II 3008 8-port SAS 12Gb/s HBA card ASUS PIKE II 3108 8-port SAS HW 12Gb/s RAID card                                                                                                                                                |  |  |

| Model Name                     | RS520A-E11-RS24U                                               |  |  |

|--------------------------------|----------------------------------------------------------------|--|--|

|                                | 24 x 2.5" hot-swap drive bays                                  |  |  |

| Ober 1940                      | - 24 x NVMe or                                                 |  |  |

| Storage Bays Front Storage Bay | - 16 x NVMe + 8x SAS/SATA(from pike card) or                   |  |  |

| ,-                             | - 12 x NVMe + 12x SAS/SATA                                     |  |  |

|                                | * SAS support only from optional SAS HBA/RAID card             |  |  |

|                                | 1 x Dual Port Intel® I350-AM2 Gigabit LAN controller           |  |  |

| Networking                     | 1 x Management Port                                            |  |  |

|                                | Optional OCP Adapter:                                          |  |  |

|                                | Up to 100Gb/s Ethernet / InfiniBand Adapter                    |  |  |

| VGA                            | Aspeed AST2600 64MB                                            |  |  |

| Graphic                        | Up to 2 x Dual slot or 4 x Single slot GPU cards supported     |  |  |

| Front I/O Ports                | 2 x USB 3.2 Gen1 ports                                         |  |  |

|                                | 2 x USB 3.2 Gen1 ports                                         |  |  |

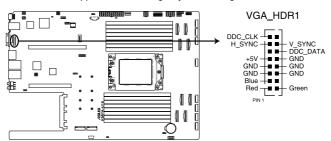

| Rear I/O Ports                 | 1 x VGA port                                                   |  |  |

| rical ino rolls                | 1 x RJ-45 Mgmt LAN port                                        |  |  |

|                                | 2 x RJ-45 1GbE LAN ports                                       |  |  |

|                                | Front Switch/LED:                                              |  |  |

|                                | 1 x Power Switch (w/ LED)                                      |  |  |

|                                | 1 x Reset Switch                                               |  |  |

|                                | 1 x Location Switch (w/ LED)                                   |  |  |

|                                | 1 x HDD Access LED                                             |  |  |

|                                | 1 x Message LED                                                |  |  |

| Switch/LED                     | LAN 1-2 LED                                                    |  |  |

|                                | Rear Switch/LED:                                               |  |  |

|                                | 1 x Port80 LED (Q-Code)                                        |  |  |

|                                | 1 x Power Switch w/ LED                                        |  |  |

|                                | 1 x Location Switch w/ LED                                     |  |  |

|                                | 1 x Message LED                                                |  |  |

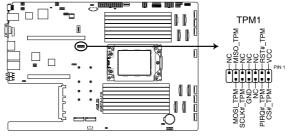

| 0 "0"                          | TPM-SPI                                                        |  |  |

| Security Options               | PFR                                                            |  |  |

|                                | Windows® Server 2019 64 bit                                    |  |  |

|                                | Windows® Server 2016                                           |  |  |

|                                | RedHat® Enterprise Linux                                       |  |  |

| OS Support                     | SuSE® Linux Enterprise Server                                  |  |  |

|                                | CentOS                                                         |  |  |

|                                | Ubuntu                                                         |  |  |

|                                | VMware                                                         |  |  |

|                                | * Please find the latest OS support from https://www.asus.com/ |  |  |

| Model Name                                                            |                      | RS520A-E11-RS24U                                                                                                                   |  |  |

|-----------------------------------------------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Management Out of Band                                                |                      | ASUS Control Center                                                                                                                |  |  |

|                                                                       |                      | On-Board ASMB10-iKVM for KVM-over-IP                                                                                               |  |  |

| Regulatory Co                                                         | mpliance             | BSMI, CE, RCM, FCC(Class A)                                                                                                        |  |  |

| Dimension                                                             |                      | 840mm x 449mm x 88.1mm (2U)                                                                                                        |  |  |

|                                                                       |                      | 33.07in x 17.68in x 3.47in                                                                                                         |  |  |

| Net Weight Kg<br>HDD not inclu                                        | (CPU, DRAM &<br>ded) | 28.74 Kg                                                                                                                           |  |  |

| Gross Weight Kg (CPU, DRAM<br>& HDD not included, Packing<br>include) |                      | 35.36 Kg                                                                                                                           |  |  |

|                                                                       |                      | 1+1 Redundant 800W 80 PLUS Platinum Power Supply<br>Rating: 100-127/200-240Vac, 10A/5A (for each inlet), 50-60Hz<br>Class I        |  |  |

|                                                                       |                      | 1+1 Redundant 850W 80 PLUS Titanium Power Supply<br>Rating: 100-127/200-240Vac, 11A/5A (for each inlet), 47-63Hz<br>or 240Vdc, 4A  |  |  |

| Power Supply<br>(different configuration by region)                   |                      | 1+1 Redundant 1200W 80 PLUS Platinum Power Supply<br>Rating: 100-127/200-240Vac, 10A/8A (for each inlet), 50-60Hz<br>or 240Vdc, 6A |  |  |

|                                                                       |                      | 1+1 Redundant 1600W 80 PLUS Platinum Power Supply<br>Rating: 100-127/200-240Vac, 10A/8A (for each inlet), 50-60Hz<br>or 240Vdc, 6A |  |  |

|                                                                       |                      | 240Vdc Only for China                                                                                                              |  |  |

|                                                                       |                      | Operation temperature: 10° ~ 35°                                                                                                   |  |  |

| Environment                                                           |                      | Non operation temperature: -40° ~ 60°                                                                                              |  |  |

|                                                                       |                      | Non operation humidity: 20% ~ 90% (Non condensing)                                                                                 |  |  |

<sup>\*</sup>Specifications are subject to change without notice.

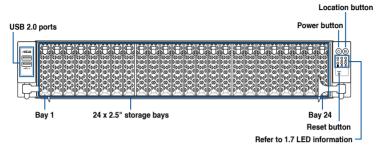

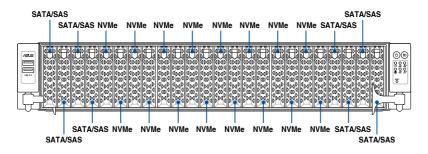

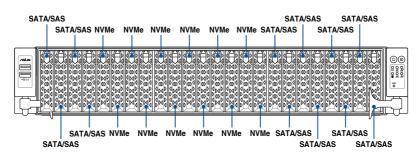

# 1.4 Front panel features

The barebone server displays a simple yet stylish front panel with easily accessible features. The power and reset buttons, LED indicators are located on the front panel.

Refer to section 1.7 LED information for the LED descriptions.

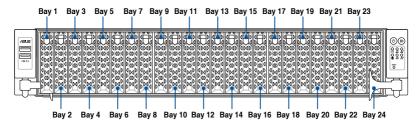

- Bay 1 to bay 24 supports NVMe for 24 NVMe configuration.

- Bay 5 to bay 20 supports NVMe; others support SATA/SAS\* from HBA/RAID for 16 NVMe configuration.

- Bay 5 to bay 16 supports NVMe, others supports SATA/SAS\* for 12 NVMe configuration.

- \* SAS support only from HBA/RAID card.

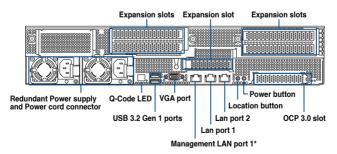

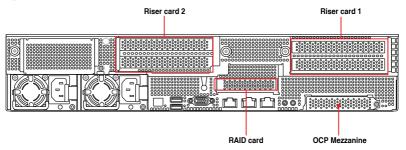

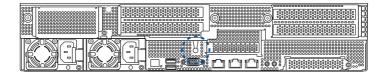

# 1.5 Rear panel features

The rear panel includes the expansion slots, and system power sockets. The middle part includes the I/O shield with openings for the rear panel connectors on the motherboard.

\*This port is for ASUS ASMB10-iKVM only.

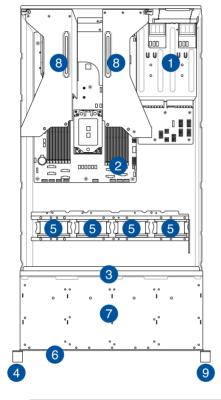

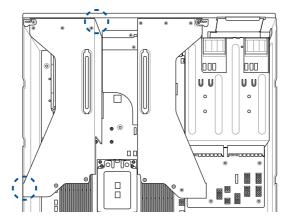

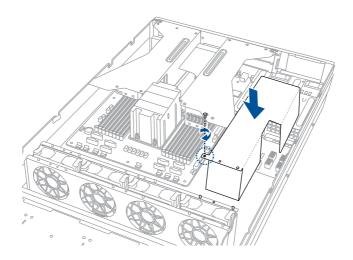

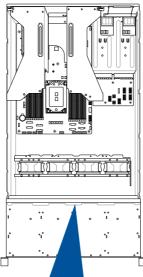

## 1.6 Internal features

The barebone server includes the basic components as shown.

- 1. Redundant Power supply

- ASUS KMPA-U16 Server Board

- 3. SATA/SAS/NVMe back panel

- 4. Front USB panel

- 5. System fans

- 6. Asset Tag (hidden)

- 7. 24 x 2.5" storage device trays

- 8. PCIe riser card **or** NVMe riser card for 24 NVMe configuration

- 9. Front I/O panel

The barebone server does not include a floppy disk drive. Connect a USB floppy disk drive to any of the USB ports on the front or rear panel if you need to use a floppy disk.

A protection film is pre-attached to the front cover before shipping. Please remove the protection film before turning on the system for proper heat dissipation.

WARNING

HAZARDOUS MOVING PARTS

KEEP FINGERS AND OTHER BODY PARTS AWAY

# 1.7 LED information

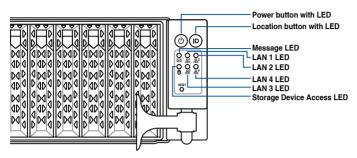

# 1.7.1 Front panel LEDs

| LED                         | lcon           | Display status | Description                              |  |

|-----------------------------|----------------|----------------|------------------------------------------|--|

| Power button with LED       | மு             | ON             | System power on                          |  |

| Storage Device              | 业              | OFF            | No activity                              |  |

| Access LED                  | ĕ              | Blinking       | Read/write data into the storage device  |  |

|                             |                | OFF            | System is normal; no incoming event      |  |

| Message LED                 | $\boxtimes$    | ON             | With the onboard ASMB10-iKVM: a          |  |

|                             |                | ON             | hardware monitor event is indicated      |  |

| ملتني محتنجم المحتنجين      |                | ON             | Location switch is pressed               |  |

| Location button with<br>LED | ID             | OFF            | Normal status (Press the location switch |  |

| LED                         |                |                | again to turn off)                       |  |

|                             | 品1             | OFF            | No LAN connection                        |  |

|                             | 品 <sup>2</sup> | Blinking       | LAN is transmitting or receiving data    |  |

| LAN LEDs                    |                | ON             |                                          |  |

|                             | 몶3             |                | LAN connection is present                |  |

|                             | 묢4             |                | ·                                        |  |

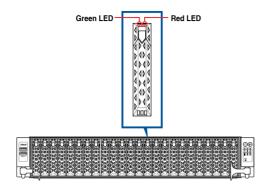

# 1.7.2 Storage device status LED

| Storage Device LED Description |          |                                                       |  |

|--------------------------------|----------|-------------------------------------------------------|--|

| Status (RED)                   | ON       | Storage device has failed                             |  |

|                                | Blinking | RAID rebuilding or locating                           |  |

|                                | ON       | Storage device power ON                               |  |

| Activity (GREEN)               | Blinking | Read/write data from/into the SATA/SAS storage device |  |

|                                | OFF      | Storage device not found                              |  |

# 1.7.3 LAN (RJ-45) LEDs

## Intel® I350-AM2 1G LAN port LEDs

| ACT/LI             | NK LED        | SPI    | ED LED              |

|--------------------|---------------|--------|---------------------|

| Status Description |               | Status | Description         |

| OFF                | No link       | OFF    | 10 Mbps connection  |

| GREEN              | Linked        | ORANGE | 100 Mbps connection |

| BLINKING           | Data activity | GREEN  | 1 Gbps connection   |

## Dedicated Management LAN port (DM\_LAN1) LED indications

| ACT/LINK LED       |               | SPEED LED |                     |  |

|--------------------|---------------|-----------|---------------------|--|

| Status Description |               | Status    | Description         |  |

| OFF                | No link       | OFF       | 10 Mbps connection  |  |

| GREEN              | Linked        | ORANGE    | 100 Mbps connection |  |

| BLINKING           | Data activity | GREEN     | 1 Gbps connection   |  |

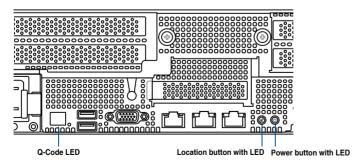

# 1.7.4 Rear panel LEDs

# 1.7.5 Q-Code table

## AMD EPYC™ 7002 Series processors

| Action       | PHASE                       | POST CODE    | TYPE     | DESCRIPTION                                                                                        |

|--------------|-----------------------------|--------------|----------|----------------------------------------------------------------------------------------------------|

| riolion      | TIMOL                       | 0x01         | Progress | First post code                                                                                    |

|              |                             | 0x02         | Progress | Load BSP microcode                                                                                 |

|              |                             | 0x03         | Progress | Perform early platform Initialization                                                              |

| SEC Start up | Security Phase              | 0x04         | Progress | Set cache as ram for PEI phase                                                                     |

|              |                             | 0x05         | Progress | Establish Stack                                                                                    |

|              |                             | 0x06         | Progress | CPU Early Initialization                                                                           |

|              |                             | 0x00         | Error    | General - Success                                                                                  |

|              |                             | 0x00         | Error    | Generic Error Code                                                                                 |

|              |                             | 0x02         | Error    | Generic Memory Error                                                                               |

|              |                             | 0x02         | Error    | Buffer Overflow                                                                                    |

|              |                             |              |          |                                                                                                    |

|              |                             | 0x04<br>0x05 | Error    | Invalid Parameter(s)                                                                               |

|              |                             | 0x05         | Error    | Invalid Data Length  Data Alignment Error                                                          |

|              |                             |              |          | <u> </u>                                                                                           |

|              |                             | 0x07         | Error    | Null Pointer Error                                                                                 |

|              |                             | 0x08         | Error    | Unsupported Function                                                                               |

|              |                             | 0x09         | Error    | Invalid Service ID                                                                                 |

|              |                             | 0x0A         | Error    | Invalid Address                                                                                    |

|              |                             | 0x0B         | Error    | Out of Resource Error                                                                              |

|              |                             | 0x0C         | Error    | Timeout                                                                                            |

|              |                             | 0x0D         | Error    | data abort exception                                                                               |

|              |                             | 0x0E         | Error    | prefetch abort exception                                                                           |

|              |                             | 0x0F         | Error    | Out of Boundary Condition Reached                                                                  |

|              |                             | 0x10         | Error    | Data corruption                                                                                    |

|              |                             | 0x11         | Error    | Invalid command                                                                                    |

|              |                             | 0x12         | Error    | The package type provided by BR is incorrect                                                       |

|              |                             | 0x13         | Error    | Failed to retrieve FW header during FW validation                                                  |

|              |                             | 0x14         | Error    | Key size not supported                                                                             |

|              |                             | 0x15         | Error    | Agesa0 verification error                                                                          |

|              |                             | 0x16         | Error    | SMU FW verification error                                                                          |

|              |                             | 0x17         | Error    | OEM SINGING KEY verification error                                                                 |

|              |                             | 0x18         | Error    | Generic FW Validation error                                                                        |

|              |                             | 0x19         | Error    | RSA operation fail - bootloader                                                                    |

|              |                             | 0x1A         | Error    | CCP Passthrough operation failed - internal status                                                 |

|              | PSP Boot Loader             | 0x1B         | Error    | AES operation fail                                                                                 |

| PSP Boot     | phase (Error Post<br>Codes) | 0x1C         | Error    | CCP state save failed                                                                              |

|              | Codes)                      | 0x1D         | Error    | CCP state restore failed                                                                           |

|              |                             | 0x1E         | Error    | SHA256 operation fail - internal status                                                            |

|              |                             | 0x1F         | Error    | ZLib Decompression operation fail                                                                  |

|              |                             | 0x20         | Error    | HMAC-SHA256 operation fail - internal status                                                       |

|              |                             | 0x21         | Error    | Booted from boot source not recognized by PSP                                                      |

|              |                             | 0x22         | Error    | PSP directory entry not found                                                                      |

|              |                             | 0x23         | Error    | PSP failed to set the write enable latch                                                           |

|              |                             | 0x24         | Error    | PSP timed out because spirom took too long                                                         |

|              |                             | 0x25         | Error    | Cannot find BIOS directory                                                                         |

|              |                             | 0x26         | Error    | SpiRom is not valid                                                                                |

|              |                             | 0x27         | Error    | slave die has different security state from master                                                 |

|              |                             | 0x28         | Error    | SMI interface init failure                                                                         |

|              |                             | 0x29         | Error    | SMI interface generic error                                                                        |

|              |                             | 0x2A         | Error    | invalid die ID executes MCM related function                                                       |

|              |                             | 0x2B         | Error    | invalid die 19 executes wickin related function  invalid MCM configuration table read from bootrom |

|              |                             | 0x2C         | Error    | Valid boot mode wasn't detected                                                                    |

|              |                             | 0x2C<br>0x2D | Error    | NVStorage init failure                                                                             |

|              |                             | 0x2E         | Error    |                                                                                                    |

|              |                             | 0x2E         | Error    | NVStorage generic error                                                                            |

|              |                             | 0x2F<br>0x30 | Error    | MCM 'error' to indicate slave has more data to send  MCM error if data size exceeds 32B            |

|              |                             |              |          | <del></del>                                                                                        |

|              |                             | 0x31         | Error    | Invalid client id for SVC MCM call                                                                 |

|              |                             | 0x32         | Error    | MCM slave status register contains bad bits                                                        |

|              |                             | 0x33         | Error    | MCM call was made in a single die environment                                                      |

|              |                             | 0x34         | Error    | PSP secure mapped to invalid segment (should be 0x400_0000)                                        |

|              |                             | 0x35         | Error    | No physical x86 cores were found on die                                                            |

|              |                             | 0x36         | Error    | Insufficient space for secure OS (range of free SRAM to SVC stack base)                            |

|              |                             | 0x37         | Error    | SYSHUB mapping memory target type is not supported                                                 |

|              |                             | 0x38         | Error    | Attempt to unmap permanently mapped TLB to PSP secure region                                       |

| Action    | PHASE                                | POST CODE    | TYPE  | DESCRIPTION                                                                                                                  |

|-----------|--------------------------------------|--------------|-------|------------------------------------------------------------------------------------------------------------------------------|

|           |                                      | 0x39         | Error | Unable to map an SMN address to AXI space                                                                                    |

|           |                                      | 0x3A         | Error | Unable to map a SYSHUB address to AXI space                                                                                  |

|           |                                      | 0x3B         | Error | The count of CCXs or cores provided by bootrom is not consistent                                                             |

|           |                                      | 0x3C         | Error | Uncompressed image size doesn't match value in compressed header                                                             |

|           |                                      | 0x3D         | Error | Compressed option used in case where not supported                                                                           |

|           |                                      | 0x3E         | Error | Fuse info on all dies don't match                                                                                            |

|           |                                      | 0x3F         | Error | PSP sent message to SMU; SMU reported an error                                                                               |

|           |                                      | 0x40         | Error | Function RunPostX86ReleaseUnitTests failed in memcmp()                                                                       |

|           |                                      | 0x41         | Error | Interface between PSP to SMU not available.                                                                                  |

|           |                                      | 0x42         | Error | Timer wait parameter too large                                                                                               |

|           |                                      | 0x43         | Error | Test harness module reported an error                                                                                        |

|           |                                      | 0x44         | Error | x86 wrote C2PMSG_0 interrupting PSP                                                                                          |

|           |                                      | 0x45         | Error | A write to an L3 register failed                                                                                             |

|           |                                      | 0x46         | Error | Mini-BL                                                                                                                      |

|           |                                      | 0x47         | Error | Mini-BL CCP HMAC Unit-test failed                                                                                            |

|           |                                      | 0x48         | Error | Potential stack corruption in jump to Mini BL                                                                                |

|           |                                      | 0x49         | Error | Error in Validate and Loading AGESA APOB SVC call                                                                            |

|           |                                      | 0x4A         | Error | Correct fuse bits for DIAG_BL loading not set                                                                                |

|           |                                      | 0x4B         | Error | The UmcProgramKeys() function was not called by AGESA                                                                        |

|           |                                      | 0x4C         | Error | Secure unlock error                                                                                                          |

|           |                                      | 0x4D         | Error | Syshub register programming mismatch during readback                                                                         |

|           |                                      | 0x4E         | Error | Family ID in MP0_SFUSE_SEC[7:3] not correct                                                                                  |

|           |                                      | 0x4F         | Error | An operation was invoked that can only be performed by the GM                                                                |

|           |                                      | 0x50         | Error | Failed to acquire host controller semaphore to claim ownership of SMB                                                        |

|           |                                      | 0x51         | Error | Timed out waiting for host to complete pending transactions                                                                  |

|           |                                      | 0x52         | Error | Timed out waiting for slave to complete pending transactions                                                                 |

|           |                                      | 0x53         | Error | Unable to kill current transaction on host                                                                                   |

|           |                                      | 0x54         | Error | One of: Illegal command                                                                                                      |

|           |                                      | 0x55         | Error | An SMBus transaction collision detected                                                                                      |

|           |                                      | 0x56         | Error | Transaction failed to be started or processed by host                                                                        |

|           |                                      | 0x57         | Error | An unsolicited SMBus interrupt was received                                                                                  |

| PSP Boot  | PSP Boot Loader<br>phase (Error Post | 0x58         | Error | An attempt to send an unsupported PSP-SMU message was made                                                                   |

| . 0. 500. | Codes)                               | 0x59         | Error | An error/data corruption detected on response from SMU for sent msg                                                          |

|           |                                      | 0x5A         | Error | MCM Steady-state unit test failed                                                                                            |

|           |                                      | 0x5B         | Error | S3 Enter failed                                                                                                              |

|           |                                      | 0x5C         | Error | AGESA BL did not set PSP SMU reserved addresses via SVC call                                                                 |

|           |                                      | 0x5E         | Error | CcxSecBisiEn not set in fuse RAM                                                                                             |

|           |                                      | 0x5F<br>0x60 | Error | Received an unexpected result  VMG Storage Init failed                                                                       |

|           |                                      | 0x60         | Error | Failure in mbedTLS user app                                                                                                  |

|           |                                      | 0x62         | Error | · · · · · · · · · · · · · · · · · · ·                                                                                        |

|           |                                      | 0x63         | Error | An error occured whilst attempting to SMN map a fuse register  Fuse burn sequence/operation failed due to internal SOC error |

|           |                                      | 0x63         | Error | Fuse sense operation timed out                                                                                               |

|           |                                      | 0x65         | Error | Fuse burn sequence/operation timed out waiting for burn done                                                                 |

|           |                                      | 0x66         | Error | Failure status indicating that the given SecureOS has been                                                                   |

|           |                                      | 0x67         | Error | This PSP FW was revoked                                                                                                      |

|           |                                      | 0x68         | Error | The platform model/vendor id fuse is not matching the BIOS public key token                                                  |

|           |                                      | 0x69         | Error | The BIOS OEM public key of the BIOS was revoked for this platform                                                            |

|           |                                      | 0x6A         | Error | PSP level 2 directory not match expected value.                                                                              |

|           |                                      | 0x6B         | Error | BIOS level 2 directory not match expected value.                                                                             |

|           |                                      | 0x6C         | Error | HVB validation failure for BIOS RTM volume (OEM public/signature failed to validate).                                        |

|           |                                      | 0x6D         | Error | Generic error indicating the CCP HAL initialization failed                                                                   |

|           |                                      | 0x94         | Error | Knoll failed to idle correctly after being reset                                                                             |

|           |                                      | 0x95         | Error | Bad status returned by I2CKnollCheck                                                                                         |

|           |                                      | 0x96         | Error | NACK to general call (no device on Knoll I2C bus)                                                                            |

|           |                                      | 0x97         | Error | Null pointer passed to I2CKnollCheck                                                                                         |

|           |                                      | 0x98         | Error | Invalid device-ID found during Knoll authentication                                                                          |

|           |                                      | 0x99         | Error | Error during Knoll/Prom key derivation                                                                                       |

|           |                                      | 0x9A         | Error | Null pointer passed to Crypto function                                                                                       |

|           |                                      | 0x9B         | Error | Error in checksum from wrapped Knoll/Prom keys                                                                               |

|           |                                      | 0x9C         | Error | Knoll returned an invalid response to a command                                                                              |

|           |                                      | 0x9D         | Error | Bootloader failed in Knoll Send Command function                                                                             |

|           |                                      | UXSD         | Error | Bootioader failed in Knoil Send Command function                                                                             |

| Action   | PHASE                                 | POST CODE | TYPE     | DESCRIPTION                                                   |

|----------|---------------------------------------|-----------|----------|---------------------------------------------------------------|

|          |                                       | 0xA0      | Progress | Bootloader successfully entered C Main                        |

| l .      |                                       | 0xA1      | Progress | Master initialized C2P / slave waited for master to init C2P  |

| l .      |                                       | 0xA2      | Progress | HMAC key successfully derived                                 |

|          |                                       | 0xA3      | Progress | Master got Boot Mode and sent boot mode to all slaves         |

| l .      |                                       | 0xA4      | Progress | SpiRom successfully initialized                               |

|          |                                       | 0xA5      | Progress | BIOS Directory successfully read from SPI to SRAM             |

|          |                                       | 0xA6      | Progress | Early unlock check                                            |

|          |                                       | 0xA7      | Progress | Inline Aes key successfully derived                           |

|          |                                       | 0xA8      | Progress | Inline-AES key programming is done                            |

|          |                                       | 0xA9      | Progress | Inline-AES key wrapper derivation is done                     |

|          |                                       | 0xAA      | Progress | Bootloader successfully loaded HW IP configuration values     |

| l .      |                                       | 0xAB      | Progress | Bootloader successfully programmed MBAT table                 |

| l .      |                                       | 0xAC      | Progress | Bootloader successfully loaded SMU FW                         |

| l .      |                                       | 0xAD      | Progress | PSP and SMU configured WAFL                                   |

|          |                                       | 0xAE      | Progress | User mode test harness completed successfully                 |

|          |                                       | 0xAF      | Progress | Bootloader loaded Agesa0 from SpiRom                          |

| l .      |                                       | 0xB0      | Progress | AGESA phase has completed                                     |

| l .      |                                       | 0xB1      | Progress | RunPostDramTrainingTests() completed successfully             |

| l .      |                                       | 0xB2      | Progress | SMU FW Successfully loaded to SMU Secure DRAM                 |

|          |                                       | 0xB3      | Progress | Sent all required boot time messages to SMU                   |

| l .      |                                       | 0xB4      | Progress | Validated and ran Security Gasket binary                      |

|          |                                       | 0xB5      | Progress | UMC Keys generated and programmed                             |

| l .      |                                       | 0xB6      | Progress | Inline AES key wrapper stored in DRAM                         |

| l .      |                                       | 0xB7      | Progress | Completed FW Validation step                                  |

| l .      |                                       | 0xB8      | Progress | Completed FW Validation step                                  |

| ı        |                                       | 0xB9      | Progress | BIOS copy from SPI to DRAM complete                           |

| ı        |                                       | 0xBA      | Progress | Completed FW Validation step                                  |

| ı        |                                       | 0xBB      | Progress | BIOS load process fully complete                              |

| PSP Boot | PSP Boot Loader<br>phase (Status Post | 0xBC      | Progress | Bootloader successfully release x86                           |

| F3F B001 | Codes)                                | 0xBD      | Progress | Early Secure Debug completed                                  |

|          |                                       | 0xBE      | Progress | GetFWVersion command received from BIOS is completed          |

|          |                                       | 0xBF      | Progress | SMIInfo command received from BIOS is completed               |

|          |                                       | 0xC0      | Progress | Successfully entered WarmBootResume()                         |

|          |                                       | 0xC1      | Progress | Successfully copied SecureOS image to SRAM                    |

|          |                                       | 0xC2      | Progress | Successfully copied trustlets to PSP Secure Memory            |

|          |                                       | 0xC3      | Progress | About to jump to Secure OS (SBL about to copy and jump)       |

|          |                                       | 0xC4      | Progress | Successfully restored CCP and UMC state on S3 resume          |

|          |                                       | 0xC5      | Progress | PSP SRAM HMAC validated by Mini BL                            |

|          |                                       | 0xC6      | Progress | About to jump to <t-base bl<="" in="" mini="" td=""></t-base> |

|          |                                       | 0xC7      | Progress | VMG ECDH unit test started                                    |

|          |                                       | 0xC8      | Progress | VMG ECDH unit test passed                                     |

|          |                                       | 0xC9      | Progress | VMG ECC CDH primitive unit test started                       |

|          |                                       | 0xCA      | Progress | VMG ECC CDH primitive unit test passed                        |

|          |                                       | 0xCB      | Progress | VMG SP800-108 KDF-CTR HMAC unit test started                  |

|          |                                       | 0xCC      | Progress | VMG SP800-108 KDF-CTR HMAC unit test passed                   |

|          |                                       | 0xCD      | Progress | VMG LAUNCH_* test started                                     |

|          |                                       | 0xCE      | Progress | VMG LAUNCH_* test passed                                      |

|          |                                       | 0xCF      | Progress | MP1 has been taken out of reset                               |

|          |                                       | 0xD0      | Progress | PSP and SMU Reserved Addresses correct                        |

|          |                                       | 0xD1      | Progress | Reached Naples steady-state WFI loop                          |

|          |                                       | 0xD2      | Progress | Knoll device successfully initialized                         |

|          |                                       | 0xD3      | Progress | 32-byte RandOut successfully returned from Knoll              |

|          |                                       | 0xD4      | Progress | 32-byte MAC successfully received from Knoll.                 |

|          |                                       | 0xD5      | Progress | Knoll device verified successfully                            |

|          |                                       | 0xD6      | Progress | Done enabling power for Knoll                                 |

|          |                                       | 0xD7      | Progress | Enter recovery mode due to trustlet validation fail.          |

|          |                                       | 0xD8      | Progress | Enter recovery mode due to OS validation fail.                |

|          |                                       | 0xD9      | Progress | Enter recovery mode due to OEM public key not found.          |

| Action      | PHASE                 | POST CODE    | TYPE                 | DESCRIPTION                                  |

|-------------|-----------------------|--------------|----------------------|----------------------------------------------|

|             |                       | 0x10         | Progress             | PEI Core Entry                               |

|             | PEI(Pre-EFI           | 0x11         | Progress             | PEI cache as ram CPU initial                 |

|             | Initialization) phase | 0x15         | Progress             | NB Initialization before installed memory    |

|             |                       | 0x19         | Progress             | SB Initialization before installed memory    |

|             |                       | 0x32         | Progress             | CPU POST-Memory Initialization               |

|             |                       | 0x33         | Progress             | CPU Cache Initialization                     |

|             |                       | 0x34         | Progress             | Application Processor(s) (AP) Initialization |

|             |                       | 0x35         | Progress             | BSP Selection                                |